IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re application of

Hiroaki TANAKA et al.

Serial No. (unknown)

Filed herewith

COLOR LIQUID CRYSTAL DISPLAY DEVICE AND MANUFACTURING METHOD OF THE SAME

# CLAIM FOR FOREIGN PRIORITY UNDER 35 U.S.C. 119 AND SUBMISSION OF PRIORITY DOCUMENT

Assistant Commissioner for Patents

Washington, D.C. 20231

Sir:

Attached hereto are certified copies of applicants' corresponding patent applications filed in Japan under 2000-161677 and 2001-110195, on May 31, 2000 and April 9, 2001, respectively.

Applicants herewith claim the benefit of the priority filing date of the above-identified application for the above-entitled U.S. application under the provisions of 35 U.S.C. 119.

Respectfully submitted,

YOUNG & THOMPSON

Benoît Castel

Attorney for Applicant Customer No. 000466 Registration No. 35,041 745 South 23rd Street Arlington, VA 22202 703/521-2297

【書類名】

特許願

【整理番号】

74610563

【あて先】

特許庁長官 及川 耕造 殿

【国際特許分類】

G02F 1/133

【発明の名称】

カラー液晶表示装置及びその製造方法

【請求項の数】

13

【発明者】

【住所又は居所】

東京都港区芝五丁目7番1号 日本電気株式会社内

【氏名】

橋本 官明

【発明者】

【住所又は居所】

東京都港区芝五丁目7番1号 日本電気株式会社内

【氏名】

田中 宏明

【発明者】

【住所又は居所】

東京都港区芝五丁目7番1号 日本電気株式会社内

【氏名】

坂本 道昭

【発明者】

【住所又は居所】

東京都港区芝五丁目7番1号 日本電気株式会社内

【氏名】

渡邊 貴彦

【発明者】

【住所又は居所】

鹿児島県出水市大野原町2080 鹿児島日本電気株式

会社内

【氏名】

城戸 秀作

【特許出願人】

【識別番号】

000004237

【氏名又は名称】

日本電気株式会社

【特許出願人】

【識別番号】

000181284

【氏名又は名称】

鹿児島日本電気株式会社

# 【代理人】

【識別番号】

100090158

【弁理士】

【氏名又は名称】

藤巻 正憲

【電話番号】

03-3433-4221

【先の出願に基づく優先権主張】

【出願番号】

特願2000-161677

【出願日】

平成12年 5月31日

【手数料の表示】

【予納台帳番号】

009782

【納付金額】

21,000円

【提出物件の目録】

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【包括委任状番号】

9715181

【包括委任状番号】

0011021

【プルーフの要否】

要

【書類名】

明細書

【発明の名称】

カラー液晶表示装置及びその製造方法

:

【特許請求の範囲】

【請求項1】 透明絶縁性基板上に薄膜トランジスタ、カラーフィルタ、ブラックマトリクス及び画素電極が形成されたカラーアクティブマトリクス基板を含むカラー液晶表示装置において、前記薄膜トランジスタは、ゲート電極、ゲート絶縁膜、半導体層、オーミック層、一対のソース・ドレイン電極が積層された逆スタガ構造であり、前記半導体層に構成されるチャネル領域上において、前記オーミック層、前記ソース・ドレイン電極及び前記ブラックマトリクスが、前記積層方向から見て同一形状であることを特徴とするカラー液晶表示装置。

【請求項2】 透明絶縁性基板上に薄膜トランジスタ、カラーフィルタ、ブラックマトリクス及び画素電極が形成されたカラーアクティブマトリクス基板を含むカラー液晶表示装置において、前記薄膜トランジスタは、ゲート電極、ゲート絶縁膜、半導体層、オーミック層、一対のソース・ドレイン電極が積層された逆スタガ構造であり、前記オーミック層と前記ソース・ドレイン電極は前記積層方向から見て同一形状であることを特徴とするカラー液晶表示装置。

【請求項3】 前記ドレイン電極につながるドレインバスラインは、前記半導体層、前記オーミック層、前記ソース・ドレイン電極を構成する金属膜と同一の金属膜の積層構造であることを特徴とする請求項1又は2に記載のカラー液晶表示装置。

【請求項4】 前記ブラックマトリクスは、前記カラーフィルタの周縁部の少なくとも一部を覆うように形成されていることを特徴とする請求項1万至3のいずれか1項に記載のカラー液晶表示装置。

【請求項5】 透明絶縁性基板に全面に第1導電膜を形成し、ゲート電極及びゲートバスラインを形成する工程と、全面にゲート絶縁膜、半導体層、オーミック層、第2導電膜を積層し、薄膜トランジスタのアイランド及びドレインバスラインを形成する工程と、前記透明絶縁性基板上の所要領域にカラーフィルタを形成する工程と、全面に遮光膜を形成し、少なくともチャネル領域以外の前記アイランドを覆う領域と前記カラーフィルタを除く領域に前記遮光膜を残してブラ

ックマトリクスを形成する工程と、前記アイランドにおいて前記ブラックマトリクスをマスクにして前記チャネル領域に相当する領域の前記第2導電膜及び前記オーミック層を除去してドレイン電極及びソース電極を形成する工程と、全面に平坦化膜を形成し、前記ソース電極を露出するコンタクトホールを形成する工程と、全面に透明導電膜を形成し、少なくとも前記カラーフィルタに重なる領域を含むように前記ソース電極に電気的に接続される画素電極を形成する工程と、を有することを特徴とするカラー液晶表示装置の製造方法。

【請求項6】 透明絶縁性基板に全面に第1導電膜を形成し、ゲート電極及びゲートバスラインを形成する工程と、全面にゲート絶縁膜、半導体層、オーミック層、第2導電膜を積層し、階段状に形成されたフォトレジストにより前記第2導電膜、前記オーミック層、前記半導体層を所要パターンに形成して薄膜トランジスタのアイランド及びドレインバスラインを形成する工程と、さらに前記フォトレジストの薄い膜厚部分をアッシングにより除去した後、前記フォトレジストの残った部分によってチャネル領域に相当する領域の前記第2導電膜及び前記オーミック層を除去してドレイン電極及びソース電極を形成する工程と、前記透明絶縁性基板上の所要領域にカラーフィルタを形成する工程と、全面に遮光膜を形成し、少なくとも前記アイランドを覆う領域と前記カラーフィルタを除く領域に前記遮光膜を残してブラックマトリクスを形成する工程と、全面に平坦化膜を形成し、且つ前記ソース電極を露出するコンタクトホールを形成する工程と、全面に透明導電膜を形成し、且つ少なくとも前記カラーフィルタに重なる領域を含むように前記ソース電極に電気的に接続される画素電極を形成する工程と、を有することを特徴とするカラー液晶表示装置の製造方法。

【請求項7】 透明絶縁性基板に全面に第1導電膜を形成し、ゲート電極及びゲートバスラインを形成する工程と、全面にゲート絶縁膜、半導体層、オーミック層及び第2導電膜を積層し、薄膜部分と厚膜部分とからなる階段状のフォトレジストを形成する工程と、このフォトレジストをマスクとして前記第2導電膜を所要パターンに形成して薄膜トランジスタのドレイン電極、ソース電極及びドレインバスラインを形成する工程と、前記フォトレジストの前記薄膜部分をアッシングにより除去する工程と、前記フォトレジストの前記厚膜部分を前記ドレイ

ン電極、前記ソース電極及び前記ドレイン電極と前記ソース電極との間の領域を保護する形状にリフローさせる工程と、このリフローされたフォトレジストをマスクとして前記オーミック層、前記半導体層を除去して薄膜トランジスタのアイランドを形成する工程と、前記フォトレジストを除去する工程と、前記ドレイン電極及びソース電極をマスクにして前記ドレイン領域と前記ソース電極との間の領域における前記オーミック層を除去してチャネル領域を形成する工程と、前記透明絶縁性基板上の所要領域にカラーフィルタを形成する工程と、全面に遮光膜を形成し、少なくとも前記アイランドを覆う領域と前記カラーフィルタを除く領域に前記遮光膜を残してブラックマトリクスを形成する工程と、全面に平坦化膜を形成し、前記ソース電極を露出するコンタクトホールを形成する工程と、全面に透明導電膜を形成し、少なくとも前記カラーフィルタに重なる領域を含むように前記ソース電極に電気的に接続される画素電極を形成する工程と、を有することを特徴とするカラー液晶表示装置の製造方法。

【請求項8】 前記ドレイン電極及びソース電極を形成した後に、全面に透明な保護絶縁膜を形成する工程を有し、前記保護絶縁膜の上に前記カラーフィルタ及びブラックマトリクスを形成することを特徴とする請求項6又は7に記載のカラー液晶表示装置の製造方法。

【請求項9】 前記カラーフィルタは透明着色樹脂を前記透明絶縁性基板上に塗布し、露光、現像して所要のパターンに形成し、前記ブラックマトリクスは 黒色樹脂を前記透明絶縁性基板上に塗布し、露光、現像して所要のパターンに形成することを特徴とする請求項5万至8のいずれか1項に記載のカラー液晶表示装置の製造方法。

【請求項10】 前記カラーフィルタは透明着色樹脂を前記透明絶縁性基板上に印刷して所要のパターンに形成し、前記ブラックマトリクスは黒色樹脂を前記透明絶縁性基板上に塗布、露光及び現像して所要のパターンに形成するか、又は印刷により所要のパターンに形成することを特徴とする請求項5万至8のいずれか1項に記載のカラー液晶表示装置の製造方法。

【請求項11】 前記ブラックマトリクスとして黒色樹脂を塗布、露光及び現像により所要のパターンに形成するか、又は印刷により所要のパターンに形成

した後、前記カラーフィルタをインクジェットにより形成することを特徴とする 請求項5万至8のいずれか1項に記載のカラー液晶表示装置の製造方法。

【請求項12】 前記コンタクトホールを形成する工程において、前記コンタクトホールを形成すると同時に、前記ゲートバスラインの端部を露出するゲート端子部コンタクトホールと、前記ドレインバスラインの端部を露出するドレイン端子部コンタクトホールを形成し、前記透明導電膜を前記両コンタクトホール内に形成することで前記ゲートバスラインに電気的に接続されるゲート端子及び前記ドレインバスラインに電気的に接続されるドレイン端子を形成することを特徴とする請求項5乃至11のいずれか1項に記載のカラー液晶表示装置の製造方法。

【請求項13】 前記遮光膜は、前記カラーフィルタの周縁部の少なくとも 一部を覆うようにパターン形成されることを特徴とする請求項5万至12のいず れか1項に記載のカラー液晶表示装置の製造方法。

#### 【発明の詳細な説明】

[0001]

#### 【発明の属する技術分野】

本発明はカラー液晶パネル等のカラー液晶表示装置及びその製造方法に関し、特に、薄膜トランジスタ(以下、TFTという)、カラーフィルタ及び画素電極を同一基板上に搭載したカラーアクティブマトリクス基板を備えるカラー液晶表示装置及びその製造方法に関する。

[0002]

#### 【従来の技術】

近時、アクティブマトリクス型のカラー液晶表示装置においては、画素電極と、前記画素電極に印加する電圧を制御するためのTFTとがマトリクス状に配置されたアクティブマトリクス基板として、BGR(青・緑・赤)の各カラーフィルタを一体的に搭載したCOT(カラーフィルタ・オン・トランジスタアレイ)基板が用いられている。そして、このCOT基板と、このCOT基板に対向して配置される対向基板との間に液晶を挟み込み、前記画素電極と前記対向基板との間に印加する電圧により前記液晶を駆動し、前記カラーフィルタを透過した色光

によりカラー表示を行っている。

[0003]

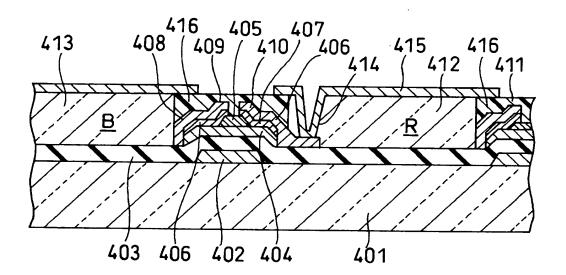

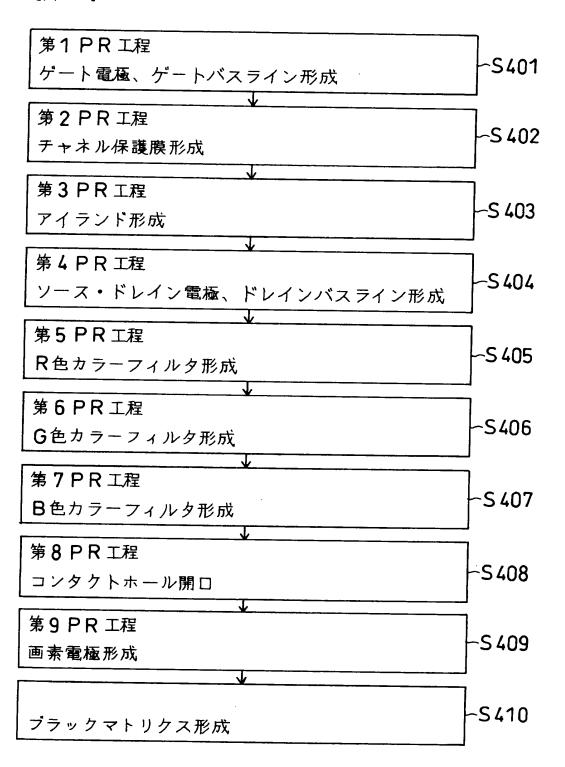

図19は、従来のCOT基板の構成の一例を示す断面図であり、特開平4-2 53028号公報に記載されているCOT基板の構成である。図20は、この従 来のCOT基板の製造方法を示す工程フロー図である。前記COT基板の構成を 、図19及び図20を参照して説明する。まず、図20のステップS401に示 すように、透明なガラス基板401の表面にゲート材料としてタンタル (Ta) 膜を形成し、第1フォトリソグラフィ工程(以下、PR工程という)により前記 タンタル膜を所要のパターンに形成してゲート電極402及びゲートバスライン (図示せず)を形成する。次いで、ステップS402に示すように、SiN $_{\mathbf{x}}$ か らなるゲート絶縁膜403を形成した後、真性a-Si膜(アモルファスシリコ ン膜)404及びチャネル保護膜405を形成し、第2PR工程により前記チャ ネル保護膜405を所要のパターンに形成する。次いで、ステップS403に示 すように、n<sup>+</sup>型a-Si膜406を形成し、n<sup>+</sup>型a-Si膜406及び真性 a-Si膜404を第3PR工程によりパターン形成してアイランド407を形 成する。次いで、ステップS404に示すように、チタン(Ti)膜408を形 成し、第4 P R 工程により前記チタン膜408を所要のパターンに形成してドレ イン電極409及びソース電極410、さらにドレインバスライン(図示せず) を形成する。

[0004]

次いで、ステップS405に示すように、全面に透明樹脂膜411を形成した上で、第5PR工程によりマスク(図示せず)を所要のパターンに形成し、このマスクを用いて透明樹脂膜411を選択的に赤色に着色してR色カラーフィルタ412を形成する。同様に、ステップS406に示すように、第6PR工程により、マスク(図示せず)を用いて透明樹脂膜411の他の領域を選択的に緑色に着色してG色カラーフィルタ(図示せず)を形成する。また、ステップS407に示すように、第7PR工程により、マスク(図示せず)を用いて透明樹脂膜410の更に他の領域を選択的に青色に着色してB色カラーフィルタ413を形成する。次いで、ステップS408に示すように、第8PR工程により、透明樹脂

膜411に、ソース電極410の一部を露出するコンタクトホール414を開口する。そして、ステップS409に示すように、全面に透明電極膜としてITO (Indium Tin Oxide) 膜を形成し、第9PR工程により前記ITO膜を各カラーフィルタ412、413、…上の領域を含む所要のパターンに形成し、コンタクトホール414を通して前記ソース電極410に電気的に接続される画素電極415を形成する。さらに、ステップS410に示すように、画素電極415を利用して、アイランド407を覆う領域における透明樹脂膜411を選択的に黒色に着色し、BM (ブラックマトリクス) 416を形成する。その後、図示は省略するが、全面に配向膜を形成し、COT基板を完成する。

# [0005]

# 【発明が解決しようとする課題】

上述のように、従来のCOT基板においては、TFTを形成する工程として、ゲート電極402、ゲート電極上のチャネル保護膜405、アイランド407、ドレイン・ソースの各電極409及び410を形成するために、第1乃至第4のPR工程、即ち、計4回のPR工程が必要とされる。また、RGB各色のカラーフィルタ412、413、…、画素電極415を形成する工程として、第5乃至第9のPR工程、即ち、計5回のPR工程が必要とされる。従って、COT基板を製造する全体の工程においてPR工程が9回必要であり、製造工程数が多く、アクティブマトリクス型カラー液晶表示装置のコスト高の要因になっている。

# [0006]

本発明はかかる問題点に鑑みてなされたものであって、製造工程数、特にPR工程数を削減し、低コスト化を実現したカラー液晶表示装置及びその製造方法を 提供することを目的とする。

# [0007]

# 【課題を解決するための手段】

本発明に係る第1のカラー液晶表示装置は、透明絶縁性基板上に薄膜トランジスタ、カラーフィルタ、ブラックマトリクス及び画素電極が形成されたカラーアクティブマトリクス基板を含むカラー液晶表示装置において、前記薄膜トランジスタは、ゲート電極、ゲート絶縁膜、半導体層、オーミック層、一対のソース・

ドレイン電極が積層された逆スタガ構造であり、前記半導体層に構成されるチャネル領域上において、前記オーミック層、前記ソース・ドレイン電極及び前記ブラックマトリクスが、前記積層方向から見て同一形状であることを特徴とする。

#### [0008]

また、本発明に係る第2のカラー液晶表示装置は、透明絶縁性基板上に薄膜トランジスタ、カラーフィルタ、ブラックマトリクス及び画素電極が形成されたカラーアクティブマトリクス基板を含むカラー液晶表示装置において、前記薄膜トランジスタは、ゲート電極、ゲート絶縁膜、半導体層、オーミック層、一対のソース・ドレイン電極が積層された逆スタガ構造であり、前記オーミック層と前記ソース・ドレイン電極は前記積層方向から見て同一形状であることを特徴とする

#### [0009]

前記第1及び第2のカラー液晶表示装置においては、前記ドレイン電極につながるドレインバスラインは、前記半導体層、前記オーミック層、前記ソース・ドレイン電極を構成する金属膜と同一の金属膜の積層構造であってもよい。また、前記ブラックマトリクスは、前記カラーフィルタの周縁部の少なくとも一部を覆うように形成されることが好ましい。

#### [0010]

本発明の第1のカラー液晶表示装置によれば、チャネル領域上においてオーミック層、ソース・ドレイン電極、ブラックマトリクスが同一平面形状であるため、これらを1回のPR工程で形成することが可能である。また、本発明の第2のカラー液晶表示装置によれば、オーミック層とソース・ドレイン電極は同一平面形状であり、両者を1回のPR工程で形成することが可能である。

#### [0011]

なお、逆スタガ構造とは、ゲート電極及びゲート絶縁膜とソース・ドレイン電極との間に半導体層を配置し、且つ、ゲート電極が下部に配置されている構造をいう。薄膜トランジスタを逆スタガ構造とすることにより、ゲート絶縁膜と半導体層を連続して成膜でき、またMOS界面の清浄化が容易となり、更にソース・ドレイン電極と半導体層との間でオーミック接触が取りやすくなる。

#### [0012]

本発明の前記第1のカラー液晶表示装置の製造方法は、透明絶縁性基板に全面に第1導電膜を形成し、ゲート電極及びゲートバスラインを形成する工程と、全面にゲート絶縁膜、半導体層、オーミック層、第2導電膜を積層し、TFTのアイランド及びドレインバスラインを形成する工程と、前記透明絶縁性基板上の所要領域に3色のカラーフィルタを形成する工程と、全面に遮光膜を形成し、少なくともチャネル領域以外の前記アイランドを覆う領域と前記カラーフィルタを除く領域に前記遮光膜を残してブラックマトリクスを形成する工程と、前記アイランドにおいて前記ブラックマトリクスをマスクにして前記チャネル領域に相当する領域の前記第2導電膜及び前記オーミック層を除去してドレイン電極及びソース電極を形成する工程と、全面に平坦化膜を形成し、前記ソース電極を露出するコンタクトホールを開口する工程と、全面に透明導電膜を形成し、少なくとも前記カラーフィルタに重なる領域を含むように前記ソース電極に電気的に接続される画素電極を形成する工程と、を有することを特徴とする。

#### [0013]

また、本発明の前記第2のカラー液晶表示装置の製造方法は、透明絶縁性基板に全面に第1導電膜を形成し、ゲート電極及びゲートバスラインを形成する工程と、全面にゲート絶縁膜、半導体層、オーミック層、第2導電膜を積層し、階段状に形成されたフォトレジストにより前記第2導電膜、前記オーミック層、前記半導体層を所要パターンに形成してTFTのアイランド及びドレインバスラインを形成する工程と、さらに前記フォトレジストの薄い膜厚部分をアッシングにより除去した後、前記フォトレジストの残った部分によってチャネル領域に相当する領域の前記第2導電膜及び前記オーミック層を除去してドレイン電極及びソース電極を形成する工程と、前記透明絶縁性基板上の所要領域に3色のカラーフィルタを形成する工程と、全面に遮光膜を形成し、少なくとも前記アイランドを覆う領域と前記カラーフィルタを除く領域に前記遮光膜を残してブラックマトリクスを形成する工程と、全面に平坦化膜を形成し、前記ソース電極を露出するコンタクトホールを開口する工程と、全面に透明導電膜を形成し、少なくとも前記カラーフィルタに重なる領域を含むように前記ソース電極に電気的に接続される画

素電極を形成する工程と、を有することを特徴とする。

[0014]

また、本発明の前記第2のカラー液晶表示装置の他の製造方法は、透明絶縁性 基板に全面に第1導電膜を形成し、ゲート電極及びゲートバスラインを形成する 工程と、全面にゲート絶縁膜、半導体層、オーミック層及び第2導電膜を積層し 、薄膜部分と厚膜部分とからなる階段状のフォトレジストを形成する工程と、こ のフォトレジストをマスクとして前記第2導電膜を所要パターンに形成して薄膜 トランジスタのドレイン電極、ソース電極及びドレインバスラインを形成する工 程と、前記フォトレジストの前記薄膜部分をアッシングにより除去する工程と、 前記フォトレジストの前記厚膜部分を前記ドレイン電極、前記ソース電極及び前 記ドレイン電極と前記ソース電極との間の領域を保護する形状にリフローさせる 工程と、このリフローされたフォトレジストをマスクとして前記オーミック層、 前記半導体層を除去して薄膜トランジスタのアイランドを形成する工程と、前記 フォトレジストを除去する工程と、前記ドレイン電極及びソース電極をマスクに して前記ドレイン領域と前記ソース電極との間の領域における前記オーミック層 を除去してチャネル領域を形成する工程と、前記透明絶縁性基板上の所要領域に カラーフィルタを形成する工程と、全面に遮光膜を形成し、少なくとも前記アイ ランドを覆う領域と前記カラーフィルタを除く領域に前記遮光膜を残してブラッ クマトリクスを形成する工程と、全面に平坦化膜を形成し、前記ソース電極を露 出するコンタクトホールを形成する工程と、全面に透明導電膜を形成し、少なく とも前記カラーフィルタに重なる領域を含むように前記ソース電極に電気的に接 続される画素電極を形成する工程と、を有することを特徴とする。

[0015]

なお、前記第2のカラー液晶表示装置の製造方法においては、前記ドレイン電極及びソース電極を形成した後に、全面に透明な保護絶縁膜を形成する工程を含み、前記保護絶縁膜の上に前記カラーフィルタ及びブラックマトリクスを形成することが好ましい。

[0016]

本発明の前記第1及び第2のカラー液晶表示装置の製造方法においては、前記

カラーフィルタは夫々の透明着色樹脂を前記透明絶縁性基板上に塗布し、露光、現像を行って所要のパターンに形成し、前記ブラックマトリクスは黒色樹脂を前記透明絶縁性基板上に塗布し、露光、現像を行って所要のパターンに形成してもよい。また、異なる製造方法として、前記カラーフィルタは透明着色樹脂を前記透明絶縁性基板上に印刷して所要のパターンに形成し、前記ブラックマトリクスは黒色樹脂を前記透明絶縁性基板上に塗布、露光、現像して所要のパターンに形成してもよく、黒色樹脂を印刷することにより所要のパターンに形成してもよい。更に、前記ブラックマトリクスとして黒色樹脂を塗布、露光、現像又は印刷により所要のパターンに形成した後、前記カラーフィルタをインクジェットにより形成してもよい。

#### [0017]

さらに、本発明の前記第1及び第2のカラー液晶表示装置の製造方法においては、前記コンタクトホールを開口すると同時に、前記ゲートバスラインの端部を露出するゲート端子部コンタクトホールと、前記ドレインバスラインの端部を露出するドレイン端子部コンタクトホールを形成し、前記透明導電膜の一部により前記ゲートバスラインに電気的に接続されるゲート端子及び前記ドレインバスラインに電気的に接続されるゲート端子及び前記ドレインバスラインに電気的に接続されるドレイン端子を形成してもよい。また、前記遮光膜は、前記カラーフィルタの少なくとも一部の周縁部においては、この周縁部を覆うようにパターン形成して前記ブラックマトリクスを形成することが好ましい。更に、前記3色のカラーフィルタは夫々の透明着色樹脂を前記透明絶縁性基板上に塗布し、かつ露光、現像して所要のパターンに形成し、前記ブラックマトリクスは黒色樹脂を前記透明絶縁性基板上に塗布し、かつ露光、現像して所要のパターンに形成してもよい。

#### [0018]

本発明の製造方法によれば、本発明の前記第1及び第2のカラー液晶表示装置のいずれも、8回のPR工程で製造することが可能になり、PR工程数の削減に伴う低コスト化が実現できる。また、カラーフィルタ及びブラックマトリクスの形成工程において印刷法又はインクジェット法を用いた場合は、さらに3~4回のPR工程が省略でき、低コスト化を図ることができる。

# [0019]

## 【発明の実施の形態】

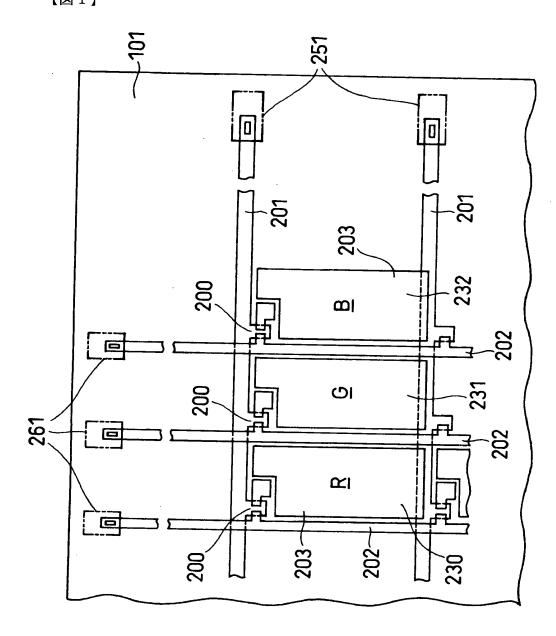

以下、本発明の実施例について添付の図面を参照して具体的に説明する。先ず、本発明の第1の実施例について説明する。図1は本実施例に係るアクティブマトリクス型カラー液晶表示装置のCOT基板の構成を示す一部概略構成図である。透明絶縁性基板101上に、互いに直交する方向に夫々所要の間隔をおいて平行に延在する夫々複数本のゲートバスライン201及びドレインバスライン202と、これらのバスラインで囲まれた領域に形成される画素電極203と、ゲートバスライン201とドレインバスライン202の交差近傍領域に形成されるTFT200とで構成されている。

#### [0020]

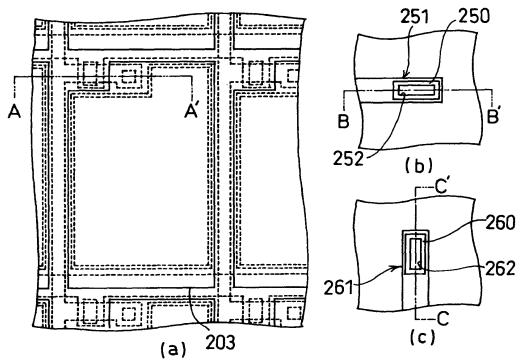

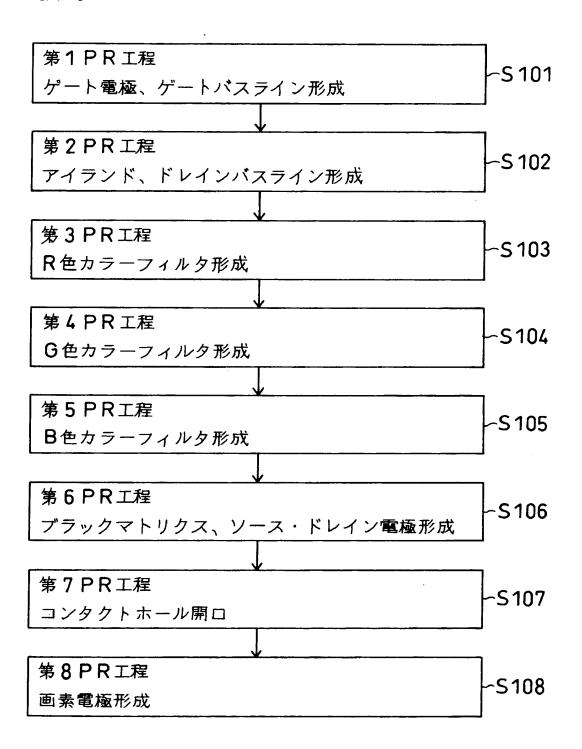

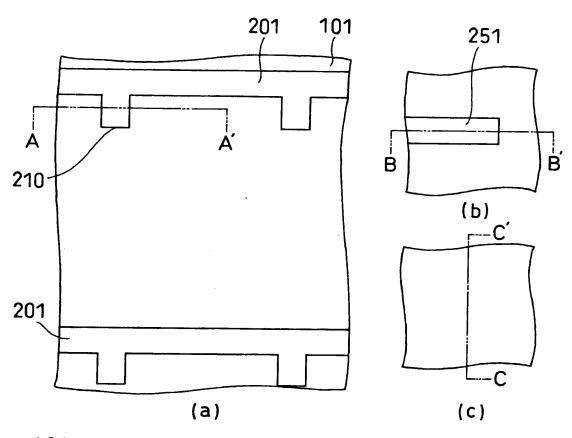

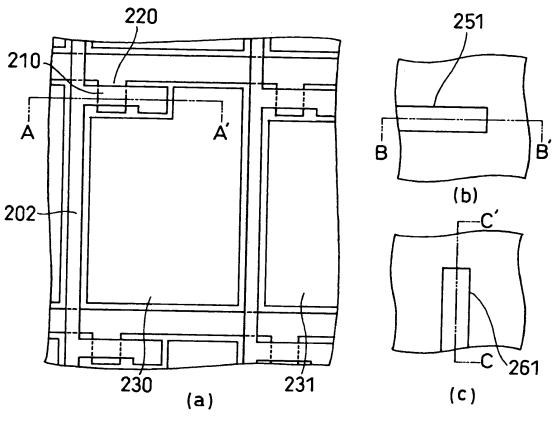

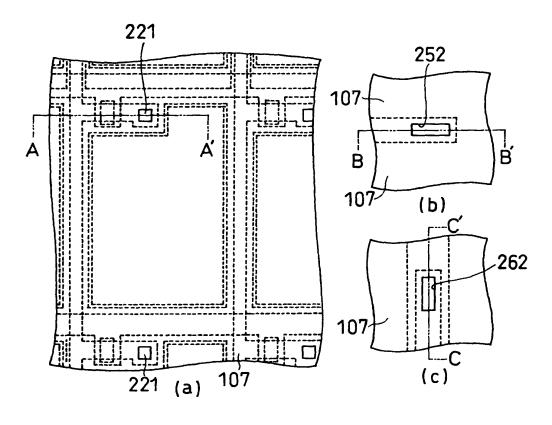

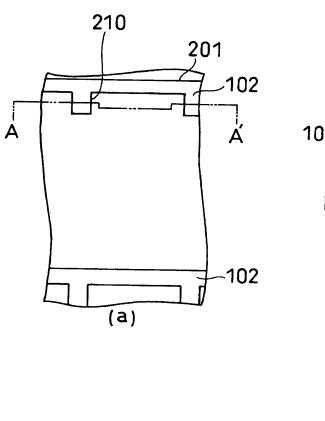

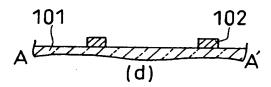

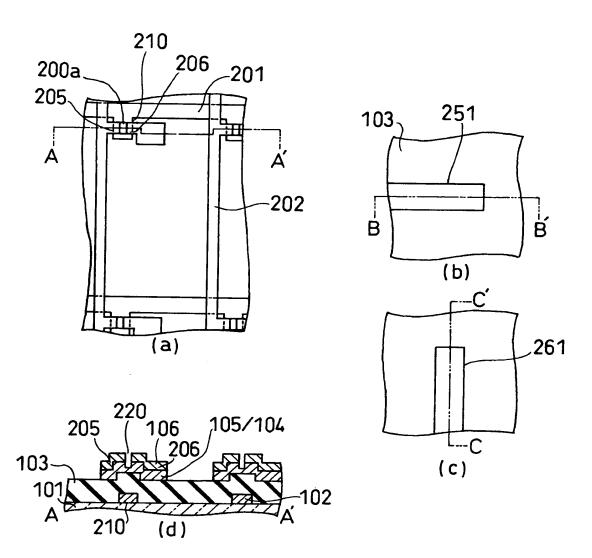

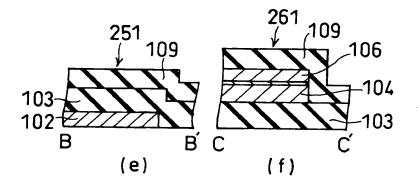

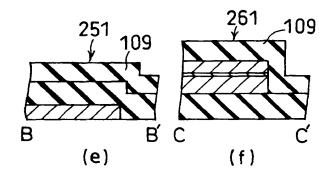

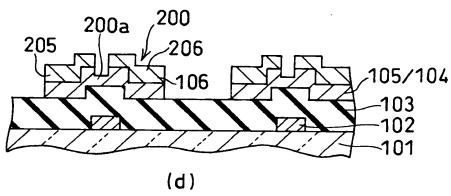

図2(a)乃至(f)は、本実施例に係るカラー液晶表示装置の構成を示す平 面図及び断面図である。図2 (a) はアクティブマトリクス基板の1画素相当領 域の平面図、(b)はゲート端子部251の平面図、(c)はドレイン端子部2 61の平面図、(d)、(e)、(f)は夫々図2(a)乃至(c)に示すAA '線、BB'線、CC'線の各断面図である。図2 (d) に示すように、TFT 200 (図1参照) においては、透明絶縁性基板101上にTi/A1膜102 から構成されるゲート電極が設けられ、このゲート電極上にSiN膜103から 構成されるゲート絶縁膜が設けられ、このゲート絶縁膜上に、このゲート絶縁膜 を介して前記ゲート電極に対向するように、真性a-Si膜104からなる半導 体層が設けられ、この半導体層上にn<sup>+</sup>型a-Si膜105からなるオーミック 層が設けられ、この上にCr膜106からなる一対のソース・ドレイン電極が設 けられている。TFT200は逆スタガ構造である。TFT200の上方及び周 囲にはブラックマトリクス240が設けられている。また、前記半導体層に構成 されるチャネル領域において、平面視で、前記オーミック層、前記ソース・ドレ イン電極及び前記ブラックマトリクスは略同一形状である。TFT200、ゲー トバスライン201、ドレインバスライン202、RGBの各カラーフィルタ2 30乃至232の上方には平坦化膜107が設けられ、平坦化膜107上におけ るRGBの各カラーフィルタ230乃至232上に相当する領域にはITO膜1

08からなる画素電極203が形成されている。また、平坦化膜107におけるソース電極206の上方にはコンタクトホール221が形成され、コンタクトホール221の内壁にITO膜108が形成されている。これにより、画素電極203がコンタクトホール221を介してソース電極206に接続されている。

## [0021]

前記ゲート電極はゲートバスライン201 (図1参照) に、前記ドレイン電極はドレインバスライン202 (図1参照) に、前記ソース電極は画素電極203 (図1参照) に夫々接続されている。また、画素電極203の直下位置には、RGBの各カラーフィルタ230乃至232が所定の配列で形成されている。また、ゲートバスライン201の一端にはゲート端子部251が、ドレインバスライン202の一端又は両端にはドレイン端子部261が夫々形成されている。

#### [0022]

図2(b)及び(e)に示すように、ゲート端子部251においては、透明絶縁性基板101上にTi/A1膜102、SiN膜103及び平坦化膜107がこの順に積層され、SiN膜103及び平坦化膜107には、ゲート端子部コンタクトホール252の内壁にはITO膜108が形成されている。このITO膜108はTi/A1膜102に接続されることにより、ゲート端子250を構成している。

#### [0023]

一方、図2(c)及び(f)に示すように、ドレイン端子部261においては、透明絶縁性基板101上に真性a-Si膜104、n<sup>+</sup>型a-Si膜105及びCr膜106がこの順に積層されている。また、この真性a-Si膜104、n<sup>+</sup>型a-Si膜105及びCr膜106の上方及び周囲には、ブラックマトリクス240及び平坦化膜107が積層されている。ブラックマトリクス240及び平坦化膜107が積層されている。ブラックマトリクス240及び平坦化膜107には、ドレイン端子部コンタクトホール262が形成され、このドレイン端子部コンタクトホール262の内壁にはITO膜108が形成されている。このITO膜108はCr膜106に接続されることにより、ゲート端子250を構成している。ゲート端子250及びドレイン端子260は透明絶縁膜基板101の側縁部(図1参照)に沿って配列されている。なお、ゲート端子

250及びドレイン端子260には、駆動回路(ドライバ、図示せず)に接続されているテープ状配線(図示せず)が接続されている。

•

#### [0024]

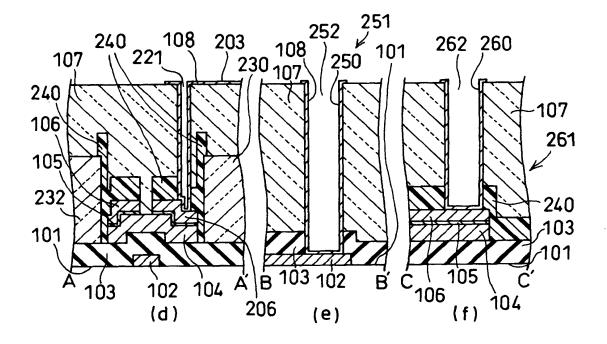

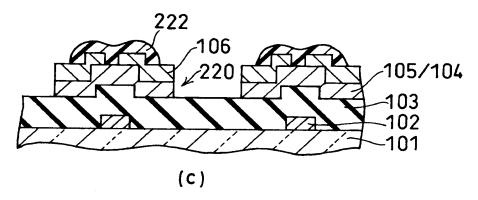

図3は本実施例に係るカラー液晶表示装置の製造方法の工程を示すフロー図である。図3に示すように、本実施例においては、第1乃至第8のPR工程によりCOT基板を製造する。即ち、ステップS101に示す第1PR工程ではゲート電極及びゲートバスラインを形成する。ステップS102に示す第2PR工程では、ゲート絶縁膜上にTFT部のアイランド及びドレインバスラインを形成する。ステップS103乃至S105に示す第3乃至第5PR工程では、画素部にRGBの各カラーフィルタを形成する。ステップS106に示す第6PR工程ではTFTのチャネル領域以外の前記アイランドを覆う領域と前記カラーフィルタを除く領域にブラックマトリクスを形成すると同時にソース・ドレイン電極を形成する。さらに、ステップS107に示す第7PR工程ではソース電極部、ゲート及びドレイン電極部にコンタクトホールを形成する。そして、ステップS108に示す第8PR工程では画素電極を形成する。

#### [0025]

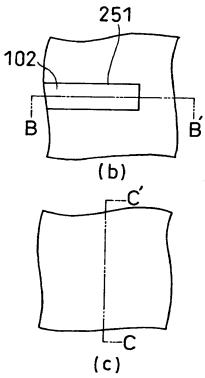

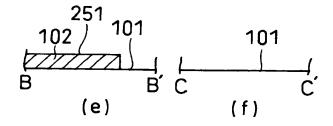

また、図4乃至8は夫々本実施例に係る液晶表示装置の製造方法における主要な工程を示す平面図及び断面図である。なお、図4乃至8及び図2の各図において、(a)はアクティブマトリクス基板の1画素相当領域の平面図、(b)はゲート端子部の平面図、(c)はドレイン端子部の平面図、(d)、(e)、(f)は夫々AA'線、BB'線、CC'線の各断面図である。以下、図2乃至8を参照して工程順に説明する。

#### [0026]

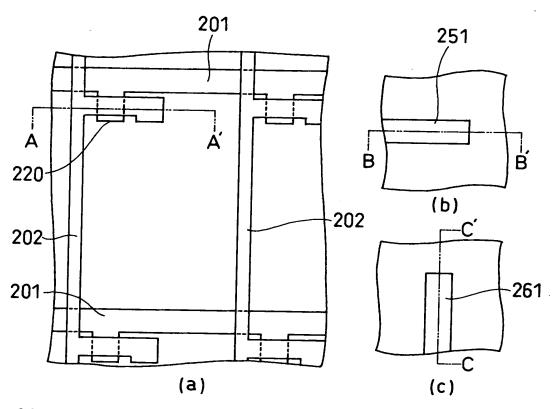

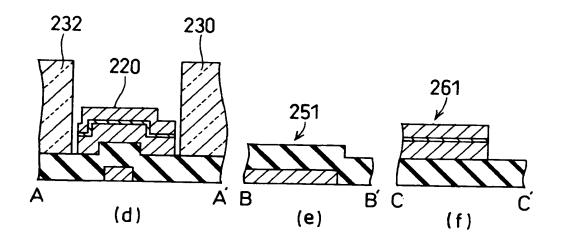

先ず、図4 (a) 乃至 (f) に示すように、ガラス等からなる透明絶縁性基板 101上に、A1とT i を積層したT i / A l 膜 10 2 をスパッタ法により0.  $1\sim0$ .  $3\mu$  m 0 厚 さに形成する。そして、第1 P R 工程において、第1 のフォトマスク (図示せず) を用いてT i / A 1 膜 1 0 2 上に第1 のフォトレジスト (図示せず) を所要のパターンに露光、現像する。次に、前記第1 のフォトレジストをマスクにしてT i / A 1 膜 1 0 2 をドライエッチングしてゲート電極2 1 0

及びゲートバスライン201を形成する。このとき、ゲートバスライン201の 端部にはゲート端子部251が形成される。

# [0027]

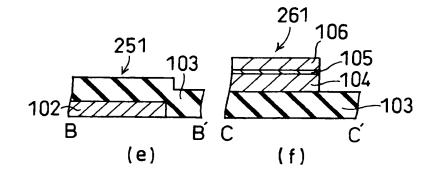

次いで、図5(a)乃至(f)に示すように、全面にゲート絶縁膜としてプラズマCVD法によりSiN膜103を0.3~0.6μmの厚さに形成する。また、その上に、半導体層として真性a-Si膜104を0.05~0.3μmの厚さに、その上にオーミック層としてリンを含むn<sup>+</sup>型a-Si膜105を20~100nmの厚さに夫々プラズマCVD法により形成する。更に、その上に、Cr膜106を0.1~0.3μm程度にスパッタ法により形成する。そして、第2PR工程において、全面に第2のフォトマスク(図示せず)を用いて、第2のフォトレジスト(図示せず)を所要のパターンに露光、現像し、前記第2のフォトレジストをマスクにして前記Cr膜106をウェットエッチングし、n<sup>+</sup>型a-Si膜105及び真性a-Si膜104を順次ドライエッチングし、ゲート電極210上にゲート絶縁膜(SiN膜103)を介してアイランド220を形成し、かつ同時にドレインバスライン202を形成する。このとき、ドレインバスライン202の端部にはドレイン端子部261が形成される。アイランド220及びドレインバスライン202は、真性a-Si膜104、n<sup>+</sup>型a-Si膜105及びCr膜106がこの順に積層されて構成されている。

## [0028]

次いで、図6(a)乃至(f)に示すように、全面に赤色の感光性アクリル樹脂を1.8μmの厚さに塗布、焼成し、第3PR工程において第3のフォトマスク(図示せず)を用いて所要パターンに露光、現像を行い、ゲートバスライン201とドレインバスライン202とで囲まれた領域のうち、選択された領域にのみ前記R色感光性アクリル樹脂を残し、R色カラーフィルタ230を形成する。同様に、全面に緑色の感光性アクリル樹脂をR色カラーフィルタ230と同じ厚さに塗布、焼成し、第4PR工程において第4のフォトマスク(図示せず)を用いて所要パターンに露光、現像を行い、ゲートバスライン201とドレインバスライン202とで囲まれた領域のうち、R色カラーフィルタ231をの選択された領域にのみ前記G色透明樹脂を残し、G色カラーフィルタ231を

形成する。さらに、全面に青色の感光性アクリル樹脂をR色カラーフィルタ230と同じ厚さに塗布、焼成し、第5PR工程において第5のフォトマスク (図示せず)を用いて所要パターンに露光、現像を行い、ゲートバスライン201とドレインバスライン202とで囲まれた領域のうち、前記R色カラーフィルタ及びG色カラーフィルタとは異なる他の残された領域にのみ前記B色透明樹脂を残し、B色カラーフィルタ232を形成する。なお、各色のカラーフィルタ230、231及び232の配置は、例えば、図1に示す配列の繰り返しとなる。

## [0029]

次いで、図7(a)乃至(f)に示すように、全面に光を透過しない黒色の感光性アクリル樹脂を1.0μmの厚さに塗布、焼成し、第6PR工程において第6のフォトマスク(図示せず)を用いて露光、現像を行い、RGBの各色カラーフィルタ230万至232以外の領域、即ち、アイランド220(図6(d)参照)上、ゲートバスライン201(図5(a)参照)上、ドレインバスライン202(図5(a)参照)上を夫々覆う領域にのみ前記黒色の感光性アクリル樹脂を形成する。これにより、前記黒色の感光性アクリル樹脂によりブラックマトリクス240が形成され、前記RGB色の各カラーフィルタ230~232を除く領域が覆われて遮光される。また、このとき、アイランド220上においては、アイランド220のほぼ中央部のチャネル領域においてブラックマトリクス240の一部を除去する。また、ゲート端子部251においてもブラックマトリクス240を除去する。なお、ドレイン端子部261においては、ブラックマトリクス240を除去する。なお、ドレイン端子部261においては、ブラックマトリクス240を除去する。なお、ドレイン端子部261においては、ブラックマトリクス240はドレインパスライン202を覆うように形成されている。

#### [0030]

次に、ブラックマトリクス240をマスクにして、その直下のCr膜106をウェットエッチング及びドライエッチングし、さらにn<sup>+</sup>型a-Si膜105をドライエッチングする。これらのエッチングにより、アイランド220(図6(d)参照)においては、Cr膜106が分離され、ドレイン電極205及びソース電極206が形成されると共に、各電極205、206の直下にn<sup>+</sup>型a-Si膜105のオーミック層が形成される。これにより、TFT200が形成される。

# [0031]

次いで、図8(a)乃至(f)に示すように、全面に平坦化膜107として、無色透明な感光性アクリル樹脂を色層の上から2.5~3.0μmの厚さに塗布、焼成する。そして、第7PR工程において、第7のフォトマスク(図示せず)を用いて露光、現像を行い、ソース電極206(図7(d)参照)上の一部、ゲート端子部251上の一部、ドレイン端子部261上の一部を夫々開口する。さらに、平坦化膜107をマスクにして、ブラックマトリクス240をドライエッチングする。さらに、ゲート端子部251において、ゲート絶縁膜を構成しているSiN膜103をドライエッチングする。これにより、前記アイランド220においてはコンタクトホール221が開口されて前記ソース電極206を構成しているCr膜106の表面が露出され、前記ゲート端子部251ではゲート端子部コンタクトホール252が開口されて前記ゲートバスライン201の一部であるTi/A1膜102が露出され、前記ドレイン端子部261ではドレイン端子部コンタクトホール262が開口されて前記ドレインバスライン202を構成しているCr膜106の表面が露出される。

# [0032]

次いで、図2(a)乃至(f)に示すように、全面に透明電極膜としてITO膜108をスパッタ法により30~100nmの厚さに形成する。そして、第8 PR工程において、ITO膜108上に第8のフォトマスク(図示せず)を用いて第8のフォトレジスト(図示せず)を所要のパターンに露光、現像した後、前記第8のフォトレジストをマスクにしてITO膜108をウェットエッチングする。これにより、RGBの各色のカラーフィルタ230~232上には、ITO膜108からなる画素電極203が形成されるとともに、この画素電極203はその一部においてコンタクトホール221を介してソース電極206に電気的に接続される。また、ITO膜108は、ゲート端子部251では、ゲート端子部コンタクトホール252を介して前記Ti/A1膜102に電気的に接続されたゲート端子250が形成される。同様に、ドレイン端子部261では、ドレイン端子部コンタクトホール262を介してCr膜106に電気的に接続され、ドレイン端子260が形成される。なお、セル工程でのギャップ制御を容易にするた

め、この後、無色透明な感光性アクリル樹脂を塗布、焼成し、第9PR工程において第9のフォトマスク(図示せず)を用いて露光、現像を行い、柱を形成して もよい。

# [0033]

その後、図示は省略するが、表面に配向膜を形成してCOT基板を形成した上で、共通電極、配向膜等が形成された対向基板を微小間隔で対向配置して一体化し、前記COT基板と前記対向基板との間に液晶を充填しかつ封止することでカラー液晶表示装置が完成される。また、前記ゲート端子、ドレイン端子には夫々ドライバ回路が電気的に接続される。

## [0034]

このように、本発明の第1の実施例においては、第1乃至第8のPR工程(柱を形成する場合には第9のPR工程)により、カラー構成のアクティブマトリクス基板を製造することが可能になる。これにより、従来の9PR工程の製造方法と比較して1PR工程の削減が実現でき、低コストなカラー液晶表示装置を提供することが可能になる。

#### [0035]

なお、本実施例においては第2PR工程においてD/I (ドレイン・アイランド) 一括エッチングを行っている。一般にD/I一括エッチングをTFT基板の製造において用いた場合は、アイランド部の段差が大きくなることにより、特にIPS (インプレインスイッチング: in plane switching) 方式のような横電界により液晶駆動を行う場合において、液晶分子の配向制御が難しくなるという問題点が生じる。また、パッシベーション膜のカバレッジが劣化するため、ソース・ドレイン電極の構成材料が液晶中に溶出し、液晶表示装置の動作中に表示シミを誘発しやすくなるという問題点が生じる。しかしながら、本実施例においては、前記アイランド部の段差をブラックマトリクス240及び平坦化膜107により覆っているため、前述の問題点を抑制することが可能である。この結果、液晶表示装置の配向制御性及び信頼性が向上する。

# [0036]

また、本発明の第1の実施例の液晶表示装置では、RGBの各色カラーフィル

タの周縁部を覆うようにブラックマトリクスが形成されるため、各カラーフィルタの周縁部の境界をブラックマトリクスによって明確にでき、鮮明な画像を表示する上で有効なものになる。ただし、本実施例では、TFTのチャネル上のブラックマトリクスを除去しているため、対向基板側にもブラックマトリクスを形成する必要がある。

# [0037]

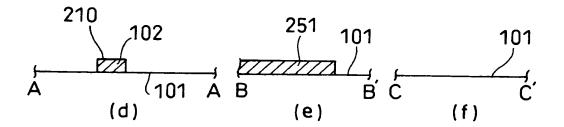

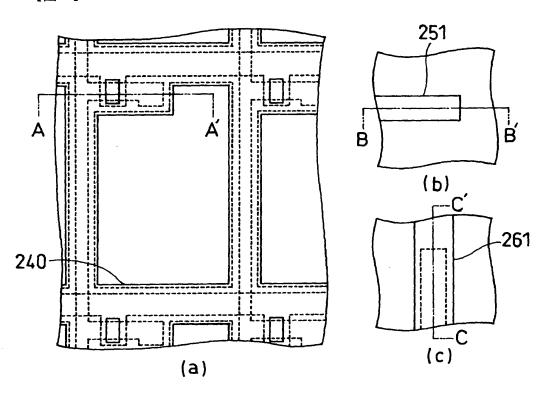

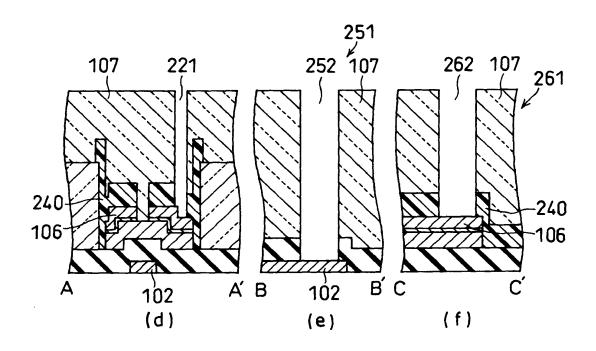

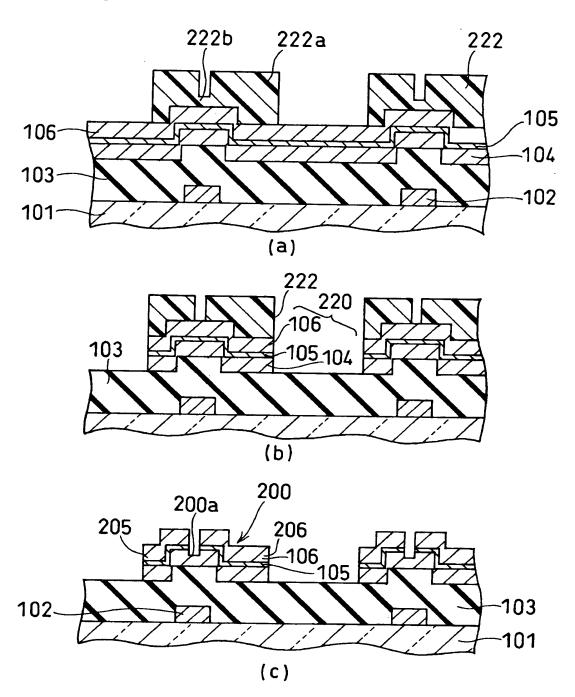

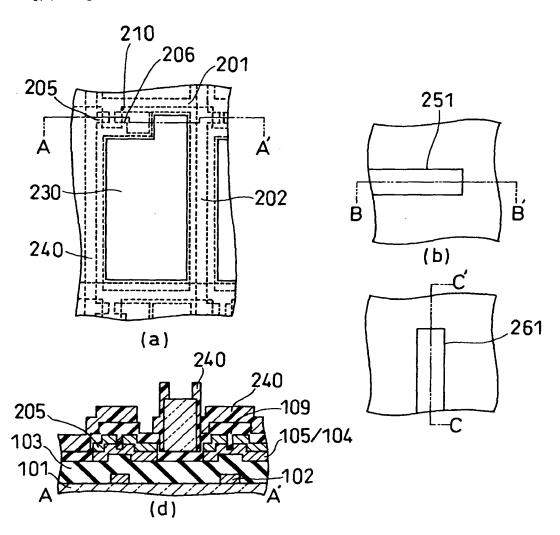

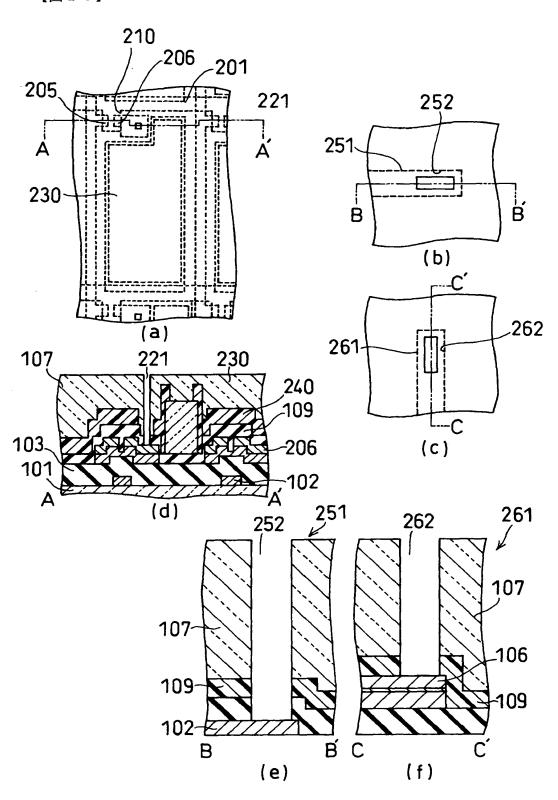

次に、本発明の第2の実施例について説明する。本実施例に係るアクティブマ トリクス型カラー液晶表示装置のCOT基板の全体構成は図1に示すCOT基板 の構成と同じである。図9 (a) 乃至 (f) は、本実施例に係るカラー液晶表示 装置の構成を示す平面図及び断面図である。図9(a)はアクティブマトリクス 基板の1画素相当領域の平面図、(b)はゲート端子部251の平面図、(c) はドレイン端子部261の平面図、(d)、(e)、(f)は夫々図9(a)乃 至(c)に示すAA'線、BB'線、CC'線の各断面図である。図9(d)に 示すように、TFT200においては、透明絶縁性基板101上にTi/A1膜 102から構成されるゲート電極が設けられ、このゲート電極上にSiN膜10 3から構成されるゲート絶縁膜が設けられ、このゲート絶縁膜上に、このゲート 絶縁膜を介して前記ゲート電極に対向するように、真性 a - S i 膜 1 0 4 からな る半導体層が設けられ、この半導体層上にn<sup>+</sup>型a-Si膜(図示せず)からな るオーミック層が設けられ、この上にCr膜106からなる一対のソース・ドレ イン電極が設けられている。TFT200の上方及び周囲にはパッシベーション 膜109が設けられ、このパッシベーション膜109上にはブラックマトリクス 240又はカラーフィルタ230乃至232が設けられている。また、前記半導 体層に構成されるチャネル領域において、平面視で、前記オーミック層と前記ソ ース・ドレイン電極とは略同一形状である。TFT200、ゲートバスライン2 01、ドレインバスライン202、RGBの各カラーフィルタ230乃至232 及びブラックマトリクス240の上方には平坦化膜107が設けられ、平坦化膜 107上におけるRGBの各カラーフィルタ230乃至232上に相当する領域 にはITO膜108からなる画素電極203が形成されている。また、平坦化膜 107におけるソース電極206の上方にはコンタクトホール221が形成され

、コンタクトホール221の内壁にITO膜108が形成されている。これにより、画素電極203がコンタクトホール221を介してソース電極206に接続されている。

[0038]

前記ゲート電極はゲートバスライン201 (図1参照)に、前記ドレイン電極はドレインバスライン202 (図1参照)に、前記ソース電極は画素電極203に夫々接続されている。また、ゲートバスライン201の一端にはゲート端子部251が、ドレインバスライン202の一端又は両端にはドレイン端子部261が夫々形成されている。

[0039]

図9(b)及び(e)に示すように、ゲート端子部251においては、透明絶縁性基板101上にTi/A1膜102、SiN膜103、パッシベーション膜109及び平坦化膜107がこの順に積層されている。SiN膜103、パッシベーション膜109及び平坦化膜107には、ゲート端子部コンタクトホール252が形成され、このゲート端子部コンタクトホール252の内壁にはITO膜108が形成されている。このITO膜108はTi/A1膜102に接続されることにより、ゲート端子250を構成している。

[0040]

一方、図9(c)及び(f)に示すように、ドレイン端子部261においては、透明絶縁性基板101上にSiN膜103が形成され、その上に真性a-Si膜104、n<sup>+</sup>型a-Si膜105及びCr膜106がこの順に積層されてドレインバスライン202を構成している。また、このドレインバスライン202の上方及び周囲には、パッシベーション膜109及び平坦化膜107が積層されている。パッシベーション膜109及び平坦化膜107には、ドレイン端子部コンタクトホール262の内壁にはITO膜108が形成されている。このITO膜108はCr膜106に接続されることにより、ドレイン端子260を構成している。ゲート端子250及びドレイン端子260には、駆動て配列されている。なお、ゲート端子250及びドレイン端子260には、駆動

回路(ドライバ、図示せず)に接続されているテープ状配線(図示せず)が接続 されている。

#### [0041]

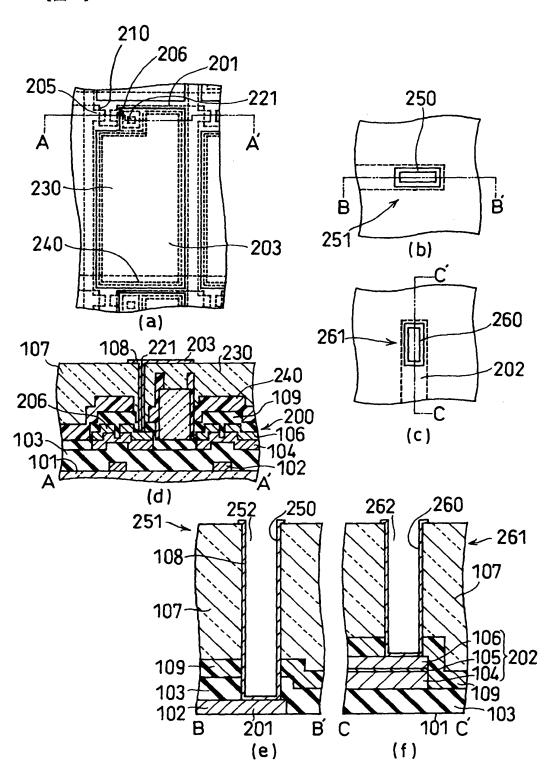

図10は本発明の第2の実施例に係る液晶表示装置の製造方法を示す工程フロー図である。図10に示すように、第2の実施例においても、前述の第1の実施例と同様に、第1乃至第8のPR工程でCOT基板を製造する。即ち、ステップS201に示す第1PR工程ではゲート電極及びゲートバスラインを形成する。ステップS202に示す第2PR工程では、ゲート絶縁膜上にTFT部のアイランドを形成した上で、後述するハーフトーン露光法又は二回露光法を利用して、ソース電極、ドレイン電極及びドレインバスラインを形成する。ステップS203乃至S205に示す第3PR工程乃至第5PR工程では、画素部にRGBの各カラーフィルタを形成する。ステップS206に示す第6PR工程では前記アイランドを覆い、且つ前記カラーフィルタを除く領域にブラックマトリクスを形成する。さらに、ステップS207に示す第7PR工程ではソース電極部、ゲート及びドレイン端子部にコンタクトホールを形成する。そして、ステップS208に示す第8PR工程では画素電極を形成する。

#### [0042]

また、図11万至15は夫々本実施例に係る液晶表示装置の製造方法における主要な工程を示す平面図及び断面図である。図11、12、14、15、16及び9の各図において、(a)はアクティブマトリクス基板の1画素相当領域の平面図、(b)はゲート端子部の平面図、(c)はドレイン端子部の平面図、(d),(e),(f)は夫々AA'線、BB'線、CC'線の各断面図である。以下、図9万至16を参照して本実施例の製造方法を工程順に説明する。なお、前述の第1の実施例と等価な部分には同一符号を付してある。

## [0043]

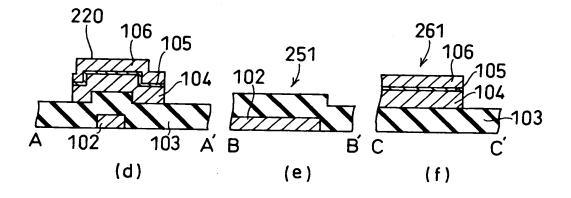

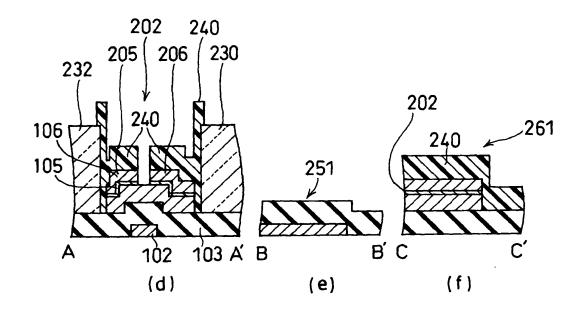

先ず、図11 (a) 乃至 (f) に示すように、ガラス等からなる透明絶縁性基板101上にA1とTiを積層したTi/A1膜102をスパッタ法により0.  $1\sim0$ .  $3\mu$ mの厚さに形成し、フォトレジスト(図示せず)を用いた第1PR 工程によりTi/A1 膜102を所要のパターンに形成してゲート電極210及

びゲートバスライン201を形成する。このとき、ゲートバスライン201の端部にはゲート端子部251が形成される。

## [0044]

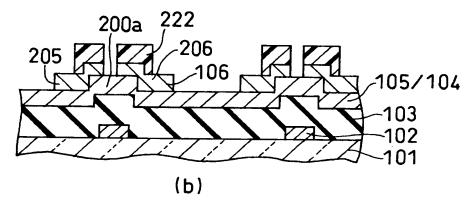

次いで、図12(a) 乃至(f) に示すように、透明絶縁性基板101及びTi/A1膜102上の全面に、ゲート絶縁膜としてプラズマCVD法によりSiN膜103を0.3~0.6  $\mu$ mの厚さに形成する。引き続き、その上に、真性a-Si膜104を0.05~0.3  $\mu$ mの厚さに、n <sup>+</sup>型a-Si膜105を20~100 nmの厚さに順次積層し、さらにその上にスパッタ法によりCr膜106を0.1~0.3  $\mu$ m程度の厚さに形成する。そして、第2PR工程において、後述するフォトレジストを用いたハーフトーン露光法により、Cr膜106、n <sup>+</sup>型a-Si膜105、真性a-Si膜104をエッチングし、ゲート電極210上に積層構造の真性a-Si膜104及びn <sup>+</sup>型a-Si膜105からなるアイランド220と、Cr膜106からなるドレイン電極205とソース電極206を形成する。また、前記ドレイン電極205につながるドレインバスライン202を形成する。このとき、ドレインバスライン202を形成する。このとき、ドレインバスライン202の端部には、前記積層構造の真性a-Si膜104及びn <sup>+</sup>型a-Si膜105とCr膜106とからなるドレイン端子部261が形成される。

# [0045]

次に、ハーフトーン露光法について説明する。図13(a)乃至(c)は、ハーフトーン露光法によるアイランド220の形成工程をその工程順に示す断面図である。フォトレジスト222を露光するためのフォトマスク(図示せず)は、ドレインバスライン202(図12(a)参照)に相当する領域は光をほぼ完全に遮断するフルマスク部として形成されるが、アイランド220に形成するTFT200のチャネル領域200aに相当する部分はハーフトーン部として構成されている。前記ハーフトーン部は、図示は省略するが、露光機の解像度限界以下の微細な遮光パターンが適宜な間隔をおいて配列された構成である。又は、前記ハーフトーン部は光透過率の低い材料により構成されている。そのため、フォトレジスト222としてポジ型フォトレジストを用いたときには、前記ハーフトーン部ではフォトレジストに対して微少な光量での露光が行われることになり、こ

のフォトレジスト222を現像したときには、前記ハーフトーン部に対応する領域222bのフォトレジスト222の膜厚はフルマスク部に対応する領域222aの膜厚よりも薄くなる。したがって、前記フォトマスクを用いてハーフトーン露光し、かつ現像した前記フォトレジストは、図13(a)に示すようにフルマスク部で露光した膜厚の厚い領域222aと、ハーフトーン部で露光した膜厚の薄い領域222bが混在する階段状の断面構造となる。

## [0046]

そして、このフォトレジスト222を用いてCr膜106をウェットエッチングし、n <sup>+</sup>型a-Si膜105、真性a-Si膜104を順次ドライエッチングすることにより、図13(b)に示すように、積層構造をしたアイランド220と、ドレインバスライン202(図12(a)参照)がパターン形成される。

# [0047]

次いで、フォトレジスト222を〇2アッシングして表面側から膜厚を低減すると、図13(b)に示すように、フォトレジスト222は、チャネル領域に相当するハーフトーン部に対応して薄く形成されている領域222bにおいては完全に除去され、下側のCr膜106が露出される。なお、前記アッシングによりフォトレジスト222の厚く形成されていた領域222aは薄くされるが、依然としてCr膜106上にマスクとして残されている。次いで、この残されているフォトレジスト222を用いてCr膜106をウェットエッチング及びドライエッチングし、さらにn<sup>+</sup>型a-Si膜105をドライエッチングすることにより、図13(c)に示すように、Cr膜106からなるドレイン電極205及びソース電極206と、その直下のn<sup>+</sup>型a-Si膜105からなるオーミック層が形成され、TFT200が形成される。即ち、1PR工程で、TFT200とドレインバスライン202が形成されることになる。

# [0048]

次いで、図14 (a) 乃至 (f) に示すように、プラズマCVD法により全面に $SiN_X$ からなる保護絶縁膜(パッシベーション膜)109を0.1  $\sim 0.3$   $\mu$  mの厚さに形成する。次に、前記第1 の実施例と同様に、透明絶縁性基板10 1 の表面上に、赤色の透明樹脂膜を0.8  $\mu$  mの厚さに形成し、第3 PR工程に

おいて所要のパターンに形成してR色カラーフィルタ230を形成する。同様に、緑色の透明樹脂膜をR色カラーフィルタ230と同じ厚さに形成し、第4PR工程において所要のパターンに形成してG色カラーフィルタ231を形成する。さらに、青色の透明樹脂膜をR色カラーフィルタ230及びG色カラーフィルタ231と同じ厚さに形成し、第5PR工程において所要のパターンに形成してB色カラーフィルタ232を形成する。各色のカラーフィルタ230乃至232の配置パターンは図1に示すとおりである。

## [0049]

そして、図15(a) 乃至(f) に示すように、光を遮光する黒色の樹脂膜を形成し、第6PR工程において、前記RGBの各カラーフィルタ領域を除く領域と、ソース電極206(図13(c)参照)の上方を除く領域を覆うようにパターン形成し、ブラックマトリクス240を形成する。なお、ブラックマトリクス240はカラーフィルタ230乃至232を形成する前に形成してもよい。

# [0050]

次いで、図16(a)乃至(f)に示すように、全面に平坦化膜107として、無色透明な感光性アクリル樹脂を2.5~3.0μmの厚さに形成した後、第7PR工程において、平坦化膜107及びパッシベーション膜109を順次選択エッチングし、ソース電極206を露出するコンタクトホール221を開口する。また、同時に前記ゲート端子部251においては平坦化膜107、パッシベーション膜109及びゲート絶縁膜103を順次選択エッチングし、ゲート端子部251におけるTi/A1膜102を露出するゲート端子部コンタクトホール252を開口する。また、ドレイン端子部261においては、平坦化膜107及びパッシベーション膜109を順次選択エッチングし、ドレイン端子部261におけるCr膜106を露出するドレイン端子部コンタクトホール262を開口する。なお、これらの端子領域には平坦化膜107を残さないようにしてもよい。

# [0051]

そして、図9 (a) 乃至 (f) に示すように、全面に透明電極膜としてスパッタ法により I T O 膜 1 O 8 を 3 O  $\sim$  1 O O n m の 厚さに形成し、第8 P R 工程により、前記 I T O 膜 1 O 8 を 各カラーフィルタ 2 3 O  $\sim$  2 3 2 上の領域を含む所

要のパターンに形成し、コンタクトホール221を通してソース電極206に電気的に接続される画素電極203を形成する。また、同時に、ITO膜108により、ゲート端子部コンタクトホール252を含む領域にゲートバスライン201に電気的に接続されたゲート端子250を形成するとともに、ドレイン端子部コンタクトホール262を含む領域にドレインバスライン202に電気的に接続されたドレイン端子260を形成する。なお、セル工程でのギャップ制御を容易にするため、第9PR工程において、さらに無色透明の感光性アクリル樹脂により柱を形成してもよい。また、第2PR工程ではハーフトーン露光法を用いる方法について述べたが、この工程においては、露光量を変え、2回露光を行う方法を用いてもよい。この場合、露光工程のみ1回増え、マスクも1枚増えるが、ハーフトーン露光法に比べプロセスの制御が容易にできるという利点がある。

#### [0052]

その後は、図示は省略するが、表面に配向膜を形成してCOT基板を形成した後、共通電極、配向膜等が形成された対向基板を微小間隔で前記COT基板に対して対向配置して一体化し、前記COT基板と前記対向基板との間に液晶を充填しかつ封止することによりカラー液晶表示装置が完成する。また、前記ゲート端子、ドレイン端子には夫々ドライバ回路が電気的に接続される。

#### [0053]

以上のように、本発明の第2の実施例においても、第1乃至第8のPR工程によりカラー構成のアクティブマトリクス基板を製造することが可能になる。これにより、従来の9PR工程の製造方法に比較して、1PR工程の削減が実現でき、低コストなカラー液晶表示装置を提供することが可能になる。また、ブラックマトリクスを従来例のように画素電極をマスクとした染色により形成したり、RGB3色の色重ねにより形成すれば、さらに1PR工程の削減が実現できる。

#### [0054]

なお、本実施例においても、前述の第1の実施例と同様に第2PR工程においてD/I(ドレイン・アイランド)一括エッチングを行っている。一般にD/I一括エッチングをTFT基板の製造において用いた場合は、アイランド部の段差が大きくなることにより、特にIPS(インプレインスイッチング:in plane s

witching)方式のような横電界により液晶駆動を行う場合において、液晶分子の配向制御が難しくなるという問題点がある。また、パッシベーション膜のカバレッジが劣化するため、ソース・ドレイン電極の構成材料が液晶中に溶出し、液晶表示装置の動作中に表示シミを誘発しやすくなるという問題点が生じる。しかしながら、本実施例においては、前記アイランド部の段差をパッシベーション膜109、ブラックマトリクス240及び平坦化膜107により覆っているため、この段差を低減することができ、前述の問題点を抑制することが可能である。この結果、液晶表示装置の配向制御性及び信頼性が向上する。

## [0055]

また、本実施例においては、ブラックマトリクスを構成するアクリルの種類として、積層構造のa-Si膜に対してブラックマトリクスが接触しても積層構造のa-Si膜を汚染するおそれがない種類のアクリルを用いた場合には、a-Si膜の汚染を防止するために設けているパッシベーション膜を省略することが可能であり、PR工程以外の工程数を削減することができる。

# [0056]

更に、本発明の第2の実施例に係る液晶表示装置においても、RGBの各色カラーフィルタの周縁部を覆うようにブラックマトリクスが形成されるため、各カラーフィルタの周縁部の境界をブラックマトリクスによって明確にでき、鮮明な画像を表示する上で有効なものになる。

#### [0057]

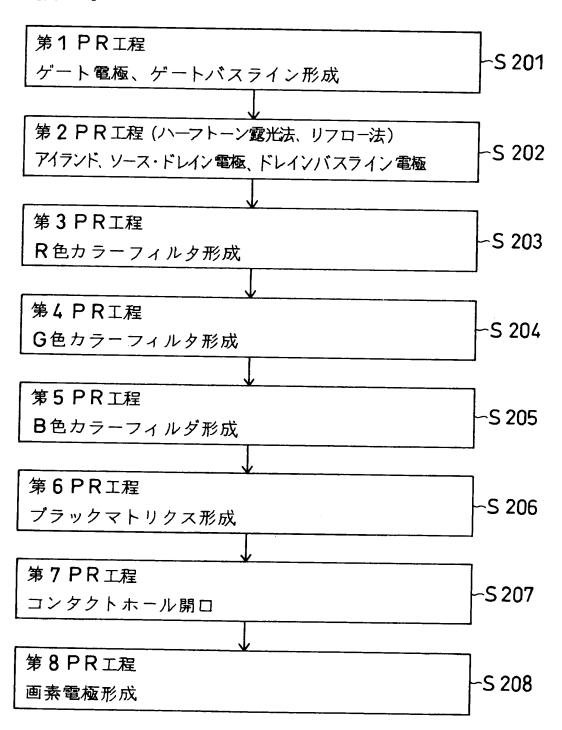

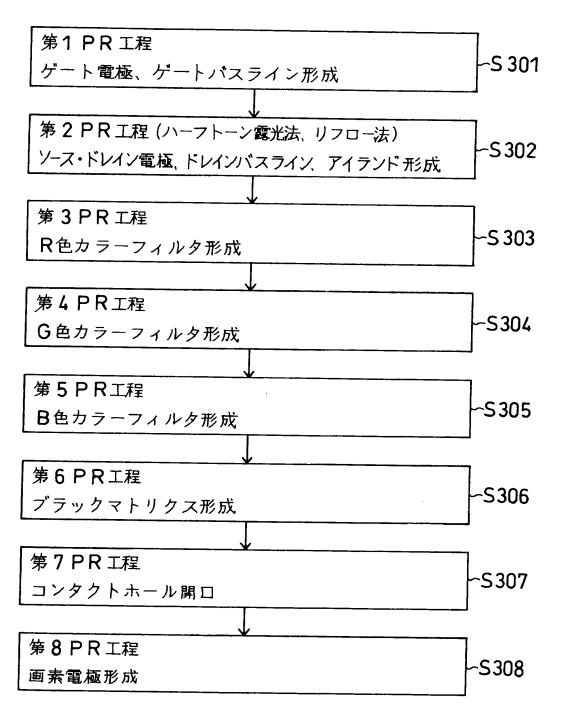

次に、本発明の第3の実施例について説明する。本実施例に係る液晶表示装置の構成は、前述の第2の実施例に係る液晶表示装置の構成と同一である。図17は本実施例に係る液晶表示装置の製造方法を示す工程フロー図である。図17に示すように、第3の実施例においても、前述の第1及び第2の実施例と同様に、第1乃至第8のPR工程でCOT基板を製造する。即ち、ステップS301に示す第1PR工程ではゲート電極及びゲートバスラインを形成する。ステップS302に示す第2PR工程では、オーミック層の上にソース電極、ドレイン電極及びドレインバスラインを形成した後、後述するハーフトーン露光法又は二回露光法とリフロー法とを利用してアイランドを形成する。ステップS303乃至S3

05に示す第3乃至第5PR工程では、画素部にRGBの各カラーフィルタを形成する。ステップS306に示す第6PR工程では前記アイランドを覆い且つ前記カラーフィルタを除く領域にブラックマトリクスを形成する。更に、ステップS307に示す第7PR工程ではソース電極部、ゲート及びドレイン端子部に夫々コンタクトホールを形成する。そして、ステップS308に示す第8PR工程では画素電極を形成する。

#### [0058]

また、図9及び図11乃至16は、前述の第2の実施例と同様に、第3の実施例に係る液晶表示装置の製造方法の主要な工程を示す平面図及び断面図である。 以下、図17並びに図9及び図11乃至16を参照して本実施例の製造方法をその工程順に説明する。

#### [0059]

先ず、図11 (a) 乃至(f) に示すように、ガラス等からなる透明絶縁性基板101上にA1とTiを積層したTi/A1膜102をスパッタ法により0.  $1\sim0$ .  $3\mu$ mの厚さに形成する。次に、フォトレジスト(図示せず)を使用する第1PR工程により、Ti/A1膜102を所要のパターンに形成してゲート電極210及びゲートバスライン201を形成する。このとき、ゲートバスライン201の端部にはゲート端子部251が形成される。

#### [0060]

次いで、図12(a) 乃至(f) に示すように、透明絶縁性基板101上の全面にゲート絶縁膜としてプラズマCVD法によりSiN膜103を0.3~0.6  $\mu$ mの厚さに形成する。引き続き、その上に、真性a-Si膜104を0.05~0.3  $\mu$ mの厚さに、n <sup>+</sup>型a-Si膜105を20~100nmの厚さに順次積層し、さらにその上にスパッタ法によりCr膜106を0.1~0.3  $\mu$ m程度の厚さに形成する。そして、第2PR工程において、後述するフォトレジストを使用するハーフトーン露光法及びリフロー法により、Cr膜106、n <sup>+</sup>型a-Si膜105、真性a-Si膜104をエッチングし、ゲート電極210上に前記積層構造のn <sup>+</sup>型a-Si膜105及び真性a-Si膜104からなるアイランド220と、Cr膜106からなるドレイン電極205及びソース電極

206と、前記ドレイン電極 205につながるドレインバスライン 202とを形成する。このとき、ドレインバスライン 202の端部には、真性 a-Si 膜 104、 n <sup>+</sup>型 a-Si 膜 105 及び Cr 膜 106 からなるドレイン端子部 261 が形成される。

[0061]

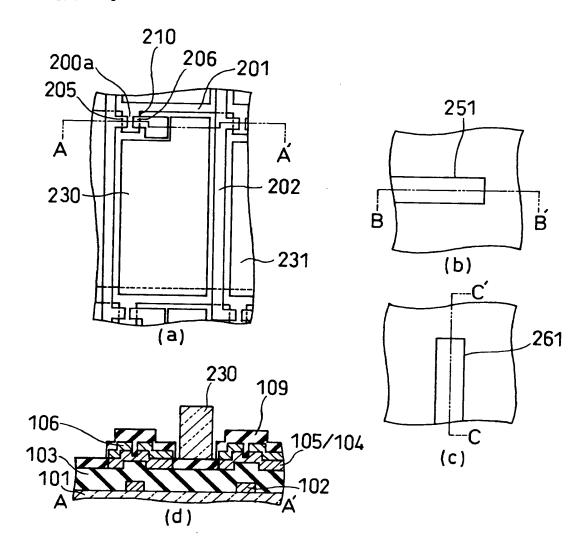

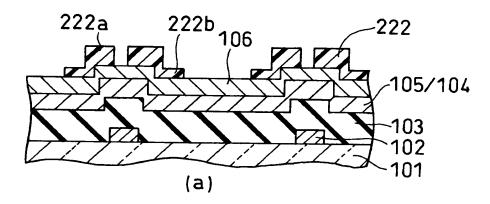

図18はハーフトーン露光法及びリフロー法によるアイランド220、ドレイ ン電極205及びソース電極206の形成工程を示す断面図を示す。フォトレジ スト222を露光するためのフォトマスク(図示せず)は、アイランド220に 形成するTFT200のチャネル領域200aを除くアイランド220の中央の 領域に相当する領域は、光をほぼ完全に遮断するフルマスク部として形成し、前 記フルマスク領域以外のアイランド220部分と、ドレインバスライン202に 相当する領域はハーフトーン部として形成する。前記ハーフトーン部は、図示は 省略するが、露光機の解像度限界以下の微細な遮光パターンが適宜な間隔をおい て配列された構成である。又は、前記ハーフトーン部は光透過率の低い材料で構 成されている。そのため、フォトレジスト222としてポジ型フォトレジストを 使用するときには、前記ハーフトーン部ではフォトレジスト222に対して微少 な光量での露光が行われることになり、露光後のフォトレジスト222を現像す ると、前記ハーフトーン部に対応する領域222bのフォトレジスト222の膜 厚はフルマスク部に対応する領域2222aの膜厚よりも薄くなる。従って、前記 フォトマスクを使用してハーフトーン露光し、かつ現像したフォトレジスト22 2の断面構造は、図18(a)に示すように、前記フォトマスクにおけるフルマ スク部で露光した膜厚の厚い領域222aと、ハーフトーン部で露光した膜厚の 薄い領域222bとが混在する階段状の断面構造となる。

[0062]

そして、このフォトレジスト222を使用してCr膜106をウェットエッチングすることにより、図18(b)に示すように、Cr膜106からなるドレイン電極205、ソース電極206及びドレインバスライン202がパターン形成される。

[0063]

次いで、フォトレジスト222をO<sub>2</sub>アッシングして表面側から膜厚を低減すると、図18(b)に示すように、フォトレジスト222は、前記ハーフトーン部に対応して薄く形成されている領域222bにおいては完全に除去され、下側のCr膜106が露出される。なお、前記アッシングによりフォトレジスト222における厚く形成された領域222aの膜厚は薄くなるが、依然としてCr膜106上にマスクとして残されている。

## [0064]

次に、この残されているフォトレジスト222に例えばNMP(Nーメチルー2ーピロリドン)のような有機溶剤の蒸気を浸透させてフォトレジスト222を変形させる有機溶剤リフロー法を使用することにより、図18(c)に示すようにチャネル領域200aを被うように前記フォトレジスト222を変形させる。次いで、この変形させたフォトレジスト222及び表面に残ったCr膜106をマスクとして、n<sup>+</sup>型a-Si膜105、真性a-Si膜104をドライエッチングすることによりアイランド220を形成する。その後、フォトレジスト222を除去し、残されたCr膜106をマスクとしてチャネル領域200aの上方に存在する n<sup>+</sup>型a-Si膜105をドライエッチングして除去することにより、ドレイン電極205及びソース電極206の直下に n<sup>+</sup>型a-Si膜105からなるオーミック層が形成され、図18(d)に示すようにTFT200が形成される。即ち、1PR工程で、TFT200とドレインバスライン202が形成されることに加え、第2の実施例と比べてエッチング工程が削減できる。

#### [0065]

次いで、図14(a)乃至(f)に示すように、プラズマCVD法により全面にSiN<sub>x</sub>からなる保護絶縁膜(パッシベーション膜)109を0.1~0.3μmの厚さに形成する。その後、前記第1の実施例と同様に、透明絶縁性基板101の表面上に、赤色の透明樹脂膜を0.8μmの厚さに形成し、第3PR工程において所要のパターンに形成してR色カラーフィルタ230を形成する。同様に、緑色の透明樹脂膜をR色カラーフィルタ230と同じ厚さに形成し、第4PR工程において所要のパターンに形成してG色カラーフィルタ231を形成する。更に、青色の透明樹脂膜をR色カラーフィルタ230及びG色カラーフィルタ

231と同じ厚さに形成し、第5PR工程において所要のパターンに形成してB 色カラーフィルタ232を形成する。各カラーフィルタ230乃至232の配置 パターンは図1に示すとおりである。

## [0066]

そして、図15(a)乃至(f)に示すように、光を遮光する黒色の樹脂膜を形成し、第6PR工程において、RGBの各カラーフィルタ230乃至232の上方に相当する領域とソース電極206(図18(b)参照)の上方に相当する領域の一部とを除く領域を覆うようにパターン形成し、ブラックマトリクス240を形成する。なお、ブラックマトリクス240はカラーフィルタ230乃至232を形成する前に形成してもよい。

#### [0067]

次いで、図16(a)乃至(f)に示すように、平坦化膜107として、無色透明な感光性アクリル樹脂を2. $5 \sim 3$ . $0 \mu$  mの厚さで全面に形成する。その後、第7PR工程において、平坦化膜107及びパッシベーション膜109を順次選択エッチングし、ソース電極206を露出するコンタクトホール221を形成する。また、同時にゲート端子部251においては、平坦化膜107、パッシベーション膜109及びゲート絶縁膜(SiN膜103)を順次選択エッチングし、ゲート端子部251を露出するゲート端子部コンタクトホール252を形成する。また、ドレイン端子部251においては、平坦化膜107及びパッシベーション膜109を順次選択エッチングし、ドレイン端子部261を露出するドレイン端子部コンタクトホール262を形成する。なお、これらの端子領域には平坦化膜107を残さないようにしてもよい。

#### [0068]

そして、図9(a)乃至(f)に示すように、全面に透明電極膜としてスパッタ法によりITO膜108を30~100nmの厚さに形成し、第8PR工程により、このITO膜108を各カラーフィルタ230乃至232上の領域を含む所要のパターンに形成し、コンタクトホール221を通してソース電極206に電気的に接続される画素電極203を形成する。また、同時に、ITO膜108により、ゲート端子部コンタクトホール252を含む領域にゲートバスライン2

01に電気的に接続されたゲート端子250を形成すると共に、ドレイン端子部コンタクトホール262を含む領域にドレインバスライン202に電気的に接続されたドレイン端子260を形成する。なお、セル工程でのギャップ制御を容易にするために、第9PR工程(図示せず)において、更に無色透明の感光性アクリル樹脂により柱を形成してもよい。また、本実施例においては、前述の第2PR工程においてハーフトーン露光法を使用する方法について説明したが、本発明においては、第2PR工程において、露光量を変えて2回の露光を行う方法を使用してもよい。

## [0069]

その後は、図示は省略するが、表面に配向膜を形成してCOT基板を形成し、 共通電極、配向膜等が形成された対向基板を、前記COT基板に対して微小間隔 を介して対向配置して一体化し、前記COT基板と前記対向基板との間に液晶を 充填して封止することにより、カラー液晶表示装置を完成する。また、ゲート端 子250及びドレイン端子260には夫々ドライバ回路が電気的に接続される。

# [0070]

本実施例においても、前述の第2の実施例と同様に第2PR工程においてD/I(ドレイン・アイランド)一括エッチングを行っている。一般にD/I一括エッチングをTFT基板の製造に用いた場合は、アイランド部の段差が大きくなることにより、特にIPS(インプレインスイッチング: in plane switching)方式のような横電界により液晶駆動を行う場合において、液晶分子の配向制御が難しくなるという問題点がある。また、パッシベーション膜のカバレッジが劣化するため、ソース・ドレイン電極の構成材料が液晶中に溶出し、液晶表示装置の動作中に表示シミを誘発しやすくなるという問題点が生じる。しかしながら、本実施例においては、前記アイランド部の段差をパッシベーション膜109、ブラックマトリクス240及び平坦化膜107により覆っているため、この段差を低減することができ、前述の問題点を抑制することが可能である。この結果、液晶表示装置の配向制御性及び信頼性が向上する。

#### [0071]

なお、前述の第2の実施例と同様に、ブラックマトリクスを構成するアクリル

として、積層構造のa-Si膜に接触したときでもこのa-Si膜を汚染するおそれがない種類のアクリルを使用する場合には、前記a-Si膜の汚染を防止するために設けているパッシベーション膜を省略することが可能である。

## [0072]

以上説明したように、本発明の第3の実施例においても、第1乃至第8のPR工程によりカラー構成のアクティブマトリクス基板を製造することが可能になる。これにより、従来の9PR工程の製造方法と比較して1PR工程の削減が実現でき、低コストなカラー液晶表示装置を提供することが可能になる。また、本発明の第3の実施例に係る液晶表示装置においても、RGBの各色カラーフィルタの周縁部を覆うようにブラックマトリクスが形成されるため、各カラーフィルタの周縁部の境界をブラックマトリクスによって明確にでき、鮮明な画像を表示することができる。

#### [0073]

上述の各実施例においては、カラーフィルタ及びブラックマトリクスを、フォトリソグラフィ法により形成する方法について説明したが、カラーフィルタ及びブラックマトリクスは印刷法により形成してもよい。また、ブラックマトリクスを従来例のように画素電極をマスクとした染色により形成したり、RGB3色の色重ねにより形成すれば、さらに1PR工程の削減が実現できる。また、ブラックマトリクスをフォトリソグラフィ法又は印刷法によって形成した後、インクジェット法によりカラーフィルタを形成してもよい。このとき、ブラックマトリクス上に撥水性の透明樹脂によるバンク材を積層し、厚さが約4μmのブラックマトリクスとバンク材を同時に又は連続してパターン形成する方法が一般的に使用されている。これらの手法を使用する場合には、更に3~4回のPR工程が省略でき、より一層の低コスト化を図ることができる。

# [0074]

なお、上述の各実施例においては、ゲート電極及びゲートバスラインにTi/A1膜を、ソース・ドレイン電極及びドレインバスラインにCr膜を用いた例を示したが、本発明はこれに限られるものではなく、前者はTi/A1/Ti膜のような3層膜、又はCr膜のような単層膜であってもよく、後者はTi/A1/

Ti膜のような3層膜であってもよい。

[0075]

#### 【発明の効果】

以上説明したように本発明のカラー液晶表示装置によれば、オーミック層、ソース・ドレイン電極、ブラックマトリクスが同一平面形状であり、又はオーミック層とソース・ドレイン電極は同一平面形状であるので、これらオーミック層、ソース・ドレイン電極、ブラックマトリクスを製造する工程を1回のPR工程で形成することが可能となり、製造工程におけるPR工程を削減することができる。そのため、本発明の製造方法によれば、本発明のカラー液晶表示装置を8回のPR工程で製造することが可能になり、PR工程数の削減に伴う低コスト化を実現できる。

#### 【図面の簡単な説明】

#### 【図1】

本発明の第1の実施例に係るアクティブマトリクス型カラー液晶表示装置のC OT基板の構成を示す一部概略構成図である。

#### 【図2】

(a) 乃至(f)は、本実施例に係るカラー液晶表示装置の構成を示す平面図及び断面図である。

#### 【図3】

本実施例に係るカラー液晶表示装置の製造方法を示す工程フロー図である。

#### 【図4】

(a) 乃至(f)は、本実施例に係るカラー液晶表示装置の製造方法を示す平面図及び断面図である。

#### 【図5】

(a) 乃至(f)は、本実施例に係るカラー液晶表示装置の製造方法において、図4に示す工程の次の工程を示す平面図及び断面図である。

#### 【図6】

(a) 乃至(f)は、本実施例に係るカラー液晶表示装置の製造方法において、図5に示す工程の次の工程を示す平面図及び断面図である。

【図7】

(a) 乃至(f) は、本実施例に係るカラー液晶表示装置の製造方法において、図6に示す工程の次の工程を示す平面図及び断面図である。

【図8】

(a) 乃至(f) は、本実施例に係るカラー液晶表示装置の製造方法において、図7に示す工程の次の工程を示す平面図及び断面図である。

【図9】

(a) 乃至(f) は、本発明の第2の実施例に係るカラー液晶表示装置の構成を示す平面図及び断面図である。

【図10】

本実施例に係るカラー液晶表示装置の製造方法を示す工程フロー図である。

【図11】

(a) 乃至(f) は、本実施例に係るカラー液晶表示装置の製造方法を示す平面図及び断面図である。

【図12】

(a) 乃至(f) は、本実施例に係るカラー液晶表示装置の製造方法において、図11に示す工程の次の工程を示す平面図及び断面図である。

【図13】

(a) 乃至(c) は、本実施例におけるハーフトーン露光法を示す断面図である。

【図14】

(a) 乃至(f) は、本実施例に係るカラー液晶表示装置の製造方法において、図12に示す工程の次の工程を示す平面図及び断面図である。

【図15】

(a) 乃至(f) は、本実施例に係るカラー液晶表示装置の製造方法において、図14に示す工程の次の工程を示す平面図及び断面図である。

【図16】

(a) 乃至(f) は、本実施例に係るカラー液晶表示装置の製造方法において、図15に示す工程の次の工程を示す平面図及び断面図である。

#### 【図17】

本発明の第3の実施例に係るカラー液晶表示装置の製造方法を示す工程フロー 図である。

. .

#### 【図18】

(a) 乃至(d) は、本実施例におけるハーフトーン露光法及びリフロー法を示す断面図である。

#### 【図19】

従来のCOT基板の一部断面図である。

#### 【図20】

従来のカラー液晶表示装置の製造方法を示す工程フロー図である。

#### 【符号の説明】

- 101;透明絶縁性基板

- 102; Ti/A1膜(ゲート電極膜)

- 103; SiN膜 (ゲート絶縁膜)

- 104;真性a-Si膜(半導体層)

- 105; n <sup>+</sup>型a-Si膜(オーミック層)

- 106; Cr膜

- 107;平坦化膜

- 108; ITO膜

- 109;パッシベーション膜

- 200; TFT

- 201;ゲートバスライン

- 202;ドレインバスライン

- 203; 画素電極

- 205;ドレイン電極

- 206;ソース電極

- 210;ゲート電極

- 220;アイランド

- 221;コンタクトホール

230乃至232;カラーフィルタ

240;ブラックマトリクス

'250;ゲート端子

251;ゲート端子部

252;ゲート端子部コンタクトホール

260;ドレイン端子

261;ドレイン端子部

262;ドレイン端子部コンタクトホール

【書類名】 図面 【図1】

【図2】

108; ITO 203; 画素電極 250; ゲート端子 260; ドレイン端子

:

#### 【図3】

【図4】

101;透明絶縁性基板 210;ゲート電極 201;ゲートバスライン

【図5】

201;ゲートパスライン 220;アイライド 202;ドレインバスライン

【図6】

230、231、232;カラーフィルタ

【図7】

【図8】

【図9】

#### 【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

e ·

#### 【図17】

# 【図18】

【図19】

;

#### 【図20】

【書類名】

要約書

【要約】

【課題】 フォトリソグラフィ工程数を削減し、低コスト化を実現するカラー液晶表示装置及びその製造方法を提供する。

【解決手段】 カラー被晶表示装置の製造方法は、透明絶縁性基板上の全面に第1導電膜を形成し、ゲート電極及びゲートバスラインを形成する第1PR工程(S101)と、全面にゲート絶縁膜、半導体層、オーミック層、第2導電膜を積層し、薄膜トランジスタのアイランド及びドレインバスラインを形成する第2PR工程(S102)と、透明絶縁性基板上の所要領域に三色のカラーフィルタを順次形成する第3乃至第5PR工程(S103~S105)と、全面に遮光膜を形成し、チャネル領域以外のアイランドを覆い且つカラーフィルタ上の領域を除く領域に前記遮光膜を残してブラックマトリクスを形成し、アイランドにおいて前記ブラックマトリクスをマスクにしてチャネル領域に相当する領域の第2導電膜及びオーミック層を除去してドレイン電極及びソース電極を形成する第6PR工程(S106)と、全面に平坦化膜を形成し、ソース電極を露出するコンタクトホールを開口する第7PR工程(S107)と、全面に透明電極を形成し、カラーフィルタに重なる領域を覆うように形成されソース電極に電気的に接続される画素電極を形成する第8PR工程(S108)とを含む。

【選択図】 図3

### 出願人履歴情報

識別番号

[000004237]

1. 変更年月日 1990年 8月29日

[変更理由]

新規登録

住 所

東京都港区芝五丁目7番1号

氏 名

日本電気株式会社

### 出 願 人 履 歴 情 報

識別番号

[000181284]

1. 変更年月日 1990年 8月10日

[変更理由] 新規登録

住 所 鹿児島県出水市大野原町2080

氏 名 鹿児島日本電気株式会社